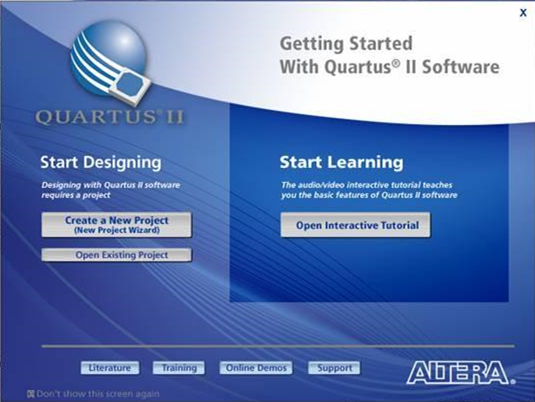

Quartus II软件介绍

Quartus II特别版是一款综合性CPLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHDL等多种设计输入形式,具有运行速度快,界面统一,功能集中,易学易用等特点,可以完成从设计输入到硬件配置的完整PLD设计流程。

Quartus II软件特色

1、采用 Spectra-Q 引擎提高您的设计效能

了解新引擎怎样减少设计迭代和编译,改变了 FPGA 设计效能的未来。

2、背景知识

现在可以 下载 新的背景知识,了解 Spectra-Q™ 引擎的详细信息。了解新引擎怎样在设计规划和实施的所有阶段提供了更多的控制功能和预测功能。您还将了解到 Spectra-Q 不仅缩短了编译时间,而且还减少了设计迭代的总次数,因此成功的解决了设计效能问题。

3、更短的编译时间

Spectra-Q 具有以下特性,编译时间和设计迭代速度提高了 8 倍,促进产品更迅速面市:

利用当今的多核工作站,算法速度更快 (综合、布局、布线、时序分析,以及物理综合)

渐进式流程支持设计人员重新进入编译阶段,逐步优化各个设计部分,显著缩短了设计迭代时间

快速重新编译特性重新使用了综合和布局布线信息,流畅的处理小的渐进式设计修改,预综合 HDL 修改的编译速度提高了 3 倍,后适配 SignalTap® II 逻辑分析器修改的编译速度提高了4倍

分布式编译支持您对设计进行划分,在服务器群的多台计算机上进行并行编译,极大的缩短了编译总时间

4、更少的设计迭代

Spectra-Q 引擎所含有的工具和功能减少了完成 FPGA 和 SoC 设计所需的设计迭代次数。

BluePrint 平台设计者 — BluePrint 平台设计者利用 Spectra-Q 新引擎来探查器件外设体系结构,高效的分配接口。BluePrint 实时进行适配以及合法检查,防止了非法引脚分配,避免了复杂的错误消息,也不需要等待全编译,I/O 设计速度提高了 10 倍。详细了解·使用 BluePrint 平台设计者 加速您的 I/O 设计。

混合布局器 — Spectra-Q 引擎还支持混合布局新特性,使用了先进的布局算法加速逻辑总体布局。混合布放器结合分析和高级退火技术,提高了结果质量,降低了种子噪声,从而加速了时序收敛。

5、更快的设计输入

还为硬件、软件和数字信号处理 (DSP) 设计人员提供了 Spectra-Q 引擎快速跟踪设计输入功能。通过多个设计输入方法,设计人员采用自己喜欢的设计环境,更高效的针对 FPGA 进行设计:

基于 C 或者 C++ — Spectra-Q 引擎支持为高级综合提供的 A++ 新编译器,从 C 或者 C++ 语言中建立知识产权 (IP) 内核,通过快速仿真和 IP 生成功能大幅度提高了效能。

基于 C (OpenCL) — 软件开发人员可以使用熟悉的基于C的设计流程和 面向 OpenCL 的 英特尔® SDK。SDK 提供软件编程模型,抽象出传统的 FPGA 硬件设计流程。

基于模型 — DSP Builder 工具 支持基于模型的设计流程:您直接在 Simulink 软件中,从您的 DSP 算法中生成 HDL。

基于 RTL — Quartus Prime 软件支持所有标准语言,包括 SystemVerilog 和 VHDL-2008。

6、为 Stratix 10 FPGA 和 SoC 提供 Spectra-Q 引擎

Stratix 10 FPGA 和 SoC 等下一代具有数百万逻辑单元 (LE) 的器件的 FPGA 设计软件需要新方法。Spectra-Q 引擎为 Quartus Prime 软件提供支持,提高 Stratix 10 器件的 设计效能,促进产品及时面市。

Stratix 10 FPGA 和 SoC 硬件实现了创新,特别是其灵活的模块化体系结构,满足了真正的分层设计需求。与 Spectra-Q 引擎一起优化而显著提高效能的关键特性包括:

新的 HyperFlex 内核体系结构,互联结构上遍布寄存器,性能比前几代 FPGA 提高了 2 倍

可编程时钟树综合

采用基于扇区的方法对器件进行配置

Spectra-Q 引擎发挥这种灵活性和模块化的优势,极大的减少了设计迭代次数,增强了设计重用,方便了体系结构探查和规划。

7、使用Spectra-Q硬划分进行IP集成演示

Spectra-Q引擎为IP重用提供了强大的新功能。例如,FPGA含有高速I/O接口,以极高的数据速率向FPGA架构传送数据。如果I/O至架构传送时序能够成功的收敛,作为单独的数据库——“硬划分”存储,那么将有利于缩短产品面市时间。这一数据库保持不变,而FPGA架构中设计的其他部分进行综合、布局和布线的多次修订。下面的视频演示了怎样在Quartus Prime Pro版软件中作为设计硬划分来建立并重用I/O至架构传送,该版软件是由Spectra-Q引擎支持的。

Quartus II软件功能

Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:

可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

芯片(电路)平面布局连线编辑;

LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;

功能强大的逻辑综合工具;

完备的电路功能仿真与时序逻辑仿真工具;

定时/时序分析与关键路径延时分析;

可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;

支持软件源文件的添加和创建,并将它们链接起来生成编程文件;

使用组合编译方式可一次完成整体设计流程;

自动定位编译错误;

高效的期间编程与验证工具;

可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;

能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。

Quartus II安装方法

一、安装必须组件

1、QuartusSetup-15.0.0.145-windows.exe

2、QuartusHelpSetup-15.0.0.145-windows.exe

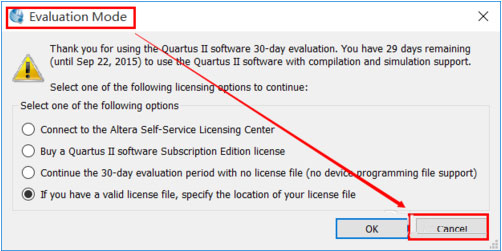

注安装后不要启动,弹出的启动界面时,选“Cancel”

二、激活

1、解压开license.zip

2、运行里面的“QuartusCrack.exe”

3、点击查找,选择"C:\altera\15.0\quartus\bin64\gcl_afcq.dll"

4、点击下一步

5、点击完成

6、启动 “Quartus II 15.0 (64-bit)”(具体的路径:C:\altera\15.0\quartus\bin64\quartus.exe)

7、在“Evaluation Mode”界面选择“if you hava a valid license file, specify the location of your license file”,点击 ok

8、获取NIC ID,如我的是:a088699e34fa , a088699e34fe , 00155d007301

9、将解压开的“license.dat”拷贝一份到 "C:\altera\15.0\licenses\license.dat", 修改其中的三处 XXXXXXXXXXXX 为自己的 NIC ID,(注意格式:如我的是 "a088699e34fa a088699e34fe 00155d007301",包括引号,中间用空格分隔)

10、选择 “C:\altera\15.0\licenses\license.dat”,点击 OK

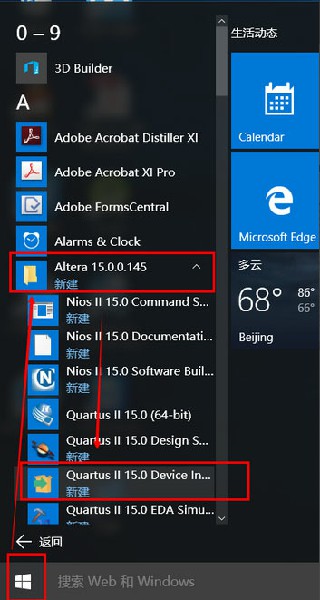

三、安装器件库

1、运行"系统开发菜单"->所有应用->Altera 15.0.0.145->Quartus II 15.0 Device Installer

2、选择刚才下载的器件库所在的目录,点击 next;

3、选择所有的复选框,点击next便开始了安装

四、安装扩展包

由于扩展包主要是 exe 可执行程序,所以安装起来也比较的简单

五、选装组件-扩展包可以安装一些扩展功能包选装组件

- 精选留言 来自吉林白山电信用户 发表于: 2023-7-10

- 很棒的软件呢。

- 精选留言 来自云南玉溪移动用户 发表于: 2023-1-27

- good~~~~~~~

- 精选留言 来自浙江湖州联通用户 发表于: 2023-11-13

- 难怪对软件的整体评价很高,真的欲罢不能

- 精选留言 来自黑龙江黑河移动用户 发表于: 2023-12-1

- 这东西太有价值了,收了收了

- 精选留言 来自河南郑州联通用户 发表于: 2023-12-8

- 明人不说暗话 我好喜欢这款软件 真的,感谢分享

浙公网安备 33038202002266号

浙公网安备 33038202002266号